電漿蝕刻簡介

電漿蝕刻是現代半導體研究與製造中的核心技術之一。隨著元件尺寸持續縮小至微米與奈米尺度,基於電漿的乾式蝕刻製程已成為不可或缺的技術,能夠提供先進微電子、奈米科技與光電元件所需的精度、結構特性以及材料選擇性。

選擇合適的電漿蝕刻技術需要考量多種因素,例如特徵尺寸、深寬比(aspect ratio)、材料系統、表面品質需求以及產能需求。本文章將提供幾種重要電漿蝕刻技術的技術概覽,包括反應離子蝕刻(Reactive Ion Etching, RIE)、感應耦合電漿反應離子蝕刻(Inductively Coupled Plasma Reactive Ion Etching, ICP-RIE)、深反應離子蝕刻(Deep Reactive Ion Etching, DRIE)以及原子層蝕刻(Atomic Layer Etching, ALE),並說明各技術的優勢、應用與在半導體研究與製造中的重要性。

了解電漿蝕刻及其運作原理

從基本原理來看,電漿蝕刻是一種乾式蝕刻製程,利用低壓電漿從基板表面去除材料。電漿由離子、自由基、電子以及中性粒子所組成,這些粒子通常由含氟或含氯等反應性氣體所產生。材料去除的過程通常是由兩種機制共同作用:物理濺射(physical sputtering)與表面化學反應(chemical reactions)。與傳統濕式化學蝕刻相比,電漿蝕刻具有更好的圖形保真度(pattern fidelity),能夠與光阻或硬式遮罩相容,並且可以對複雜的多層材料堆疊進行奈米尺度控制的蝕刻。

透過精確控制電漿製程參數,例如壓力、RF 功率、氣體組成、基板偏壓以及電漿浸入條件,工程師可以調整蝕刻速率、各向異性(anisotropy)、選擇性(selectivity)以及表面損傷程度。這些優勢使電漿蝕刻成為先進半導體元件、MEMS、光子元件以及新興量子與奈米電子技術中不可或缺的製程。

哪一種電漿蝕刻技術最好?

要回答這個問題,首先需要了解每種蝕刻技術的優勢、限制與適用領域。透過比較各製程在蝕刻速率、各向異性、材料選擇性、表面品質以及可擴展性等方面的特性,工程師才能決定最適合特定材料、元件結構與製程需求的電漿蝕刻方法。

反應離子蝕刻(RIE)與感應耦合電漿 RIE(ICP-RIE)的比較

反應離子蝕刻是如何運作的

反應離子蝕刻(RIE)是微影製程中最常使用的電漿蝕刻技術之一。在 RIE 系統中,通常採用平行板反應器結構,透過 RF 功率產生電漿並對基板施加偏壓。此偏壓會加速離子朝晶圓表面移動,透過化學反應與物理轟擊的結合產生具有方向性的蝕刻效果(各向異性蝕刻)。

為何選擇 RIE?

RIE 在化學選擇性與物理方向性之間取得良好的平衡。它可以形成具有各向異性的蝕刻輪廓,適合製作精細結構,同時硬體設備相對簡單,製程控制也較容易。RIE 系統成本較低、用途廣泛,非常適合研究實驗室與小規模製造環境。不過與高密度電漿系統相比,其蝕刻速率與電漿密度較為有限。

RIE 在半導體研究與微電子製造中應用廣泛,例如矽、二氧化矽、氮化矽、III-V 半導體以及金屬層的圖形化製程。在光電領域中,RIE 常用於製作波導、光柵以及光子晶體結構等元件。然而 RIE 也存在一些限制。傳統 RIE 系統的電漿密度較低,因此蝕刻速率有限,不適合製作深或高深寬比結構。由於離子能量與電漿密度是耦合的,當提高方向性時,往往會增加離子轟擊能量,進而造成基板損傷、遮罩侵蝕以及選擇性下降。

此外,在先進奈米尺度圖形轉移中,RIE 的製程窗口較窄,對於複雜材料堆疊的蝕刻也較具挑戰性。因此,在先進半導體製程中,RIE 越來越多被高密度電漿技術所補充或取代。

ICP-RIE 是 RIE 的進階版本,在許多 SENTECH 電漿系統中使用。ICP-RIE 系統利用感應耦合 RF 來源產生高密度電漿,同時使用另一個 RF 偏壓來控制離子能量。

ICP-RIE 的優勢為何?

ICP-RIE 的主要優勢在於其高電漿密度,使其能夠達到比傳統 RIE 更高的蝕刻速率與更精確的製程控制。由於離子通量與離子能量可以獨立控制,因此能夠實現優異的各向異性、高選擇性以及較低的基板損傷。

ICP-RIE 特別適合奈米尺度圖形轉移以及對材料損傷敏感的製程。該技術廣泛應用於先進半導體製造、奈米科技研究以及化合物半導體製程,例如高深寬比奈米結構、光子元件、GaN 與 SiC 功率電子元件,以及 LED 和雷射二極體等光電元件。然而 ICP-RIE 系統的複雜度與成本也相對較高。此外,其寬廣的製程參數空間需要專業的製程開發,這在研究環境中可能會增加開發時間。

DRIE 與低溫蝕刻的特性與應用

何時使用深反應離子蝕刻(DRIE)?

深反應離子蝕刻(DRIE)是一種專門用於製作極高深寬比結構的電漿蝕刻技術,特別適用於矽材料。DRIE 最常見的實現方式是 Bosch 製程,該製程透過交替進行蝕刻與側壁鈍化步驟,以形成接近垂直的側壁結構。DRIE 可以實現數百微米深度的蝕刻,同時保持高深寬比與良好的側壁垂直度,這是其他蝕刻技術難以達到的能力。DRIE 在 MEMS 製造中至關重要,例如深溝槽、空腔以及穿矽通孔(TSV)的製作。

低溫電漿蝕刻相較 DRIE 的優勢

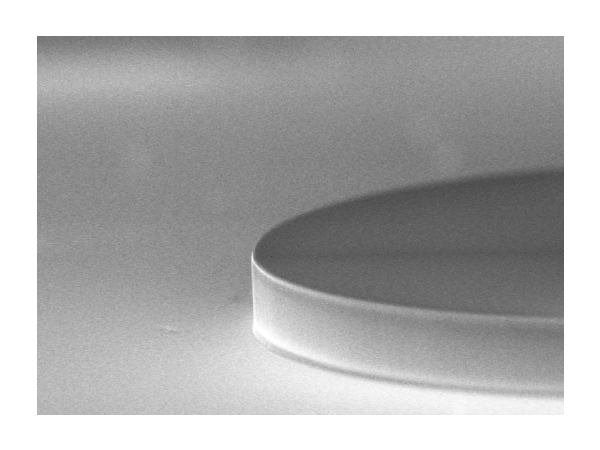

低溫電漿蝕刻是一種在極低溫條件下進行的矽蝕刻技術,通常在 −80°C 至 −140°C 的基板溫度下進行。在低溫條件下,會在側壁形成 SiOxFy 自鈍化層,從而抑制側向蝕刻並形成高度各向異性的結構。與 Bosch DRIE 不同,低溫蝕刻是連續製程,不需要聚合物鈍化步驟,因此可以得到非常平滑的側壁。這使其在矽光子學與微光學元件製作中非常有吸引力,例如矽波導、光子晶體以及高 Q 值光學共振器。

低溫電漿蝕刻的工作原理是什麼?

在低溫刻蝕中,通常使用SF₆/O₂等離子體對矽進行刻蝕,同時利用液態氮(LN₂)將晶圓冷卻至低溫。在這種條件下,氧輔助反應會在側壁上形成一層薄的SiOxFy鈍化層,抑制橫向蝕刻。同時,溝槽底部的離子轟擊會持續移除此鈍化層,使垂直方向的材料去除得以進行。離子能量、氧濃度和基板溫度之間的平衡決定了各向異性和蝕刻速率。與博世製程不同,低溫刻蝕以連續模式運行,不依賴聚合物鈍化層,因此可以獲得光滑的側壁,並且避免了循環DRIE製程中常見的扇貝狀缺陷。

低溫等離子體刻蝕的主要優勢在於能夠製造側壁粗糙度極低的垂直矽結構,而這在傳統的DRIE製程中難以實現。低溫等離子體蝕刻可以獲得高縱橫比,尤其適用於窄結構,同時保持優異的尺寸精度。這些特性使得低溫刻蝕在對錶面品質要求極高的應用領域極具吸引力。然而,低溫刻蝕需要精確控制晶圓溫度和熱均勻性,這通常透過氦氣背面冷卻和專用卡盤設計來實現。與BoschDRIE製程相比,低溫DRIE製程對圖案密度和晶圓負載效應更為敏感。此外,由於連續蝕刻機制,掩模選擇性通常較低,這會在使用光阻掩模時限制可實現的刻蝕深度。再加上光阻在低溫下機械穩定性和附著力降低,因此對於深刻蝕或高深寬比蝕刻,通常需要使用硬掩模(例如SiO₂或Si₃N₄)。

低溫等離子體刻蝕與DRIE製程結合應用於微機電系統(MEMS)、矽光子學和微光學元件製造,在這些領域,光滑的側壁和精確的特徵定義至關重要。典型應用包括矽波導、光子晶體結構、高品質因子光學諧振器和微流控通道。該技術在先進的光子和量子裝置領域重新引起了人們的關注,因為側壁粗糙度和表面損傷會顯著影響裝置性能。

什麼是原子層蝕刻(ALE)?

與其他技術相比,原子層蝕刻 (ALE) 代表了電漿蝕刻精度和控制的下一個發展階段,能夠以原子級精度去除材料。 ALE 基於自限制的、時間或化學反應限制的表面反應,透過連續的循環處理步驟,逐層精確去除材料。

ALE 的主要優勢在於對蝕刻深度、均勻性和損傷最小化的無與倫比的控制。由於每一步的材料去除量有限,ALE 最大限度地減少了變異性,並實現了埃級精度。這對於半導體技術的先進節點至關重要,因為即使是微小的偏差也會影響裝置效能。

何時應該選擇 ALE?

ALE 特別適用於先進半導體研究,例如奈米尺度的邏輯與記憶體元件。

此外,在量子元件、先進光電元件以及異質整合技術中,ALE 也越來越重要。然而 ALE 的主要限制在於其製程速度。由於每個循環只移除一層原子,因此其蝕刻速度遠低於連續式電漿蝕刻技術。

SENTECH 電漿蝕刻工具

SENTECH 電漿蝕刻系統如何支援先進研究和製造?

SENTECH 提供全面的電漿體蝕刻工具組合,可滿足半導體研究、微納加工和光電子領域的各種需求。 SENTECH 系統在設計時充分考慮了靈活性、精確性和可靠性,使用戶能夠在單一平台或模組化叢集配置中執行 RIE、ICP-RIE、DRIE 和 ALE 等製程。

SENTECH 電漿體蝕刻工具能夠精確控制等離子體密度、電漿能量、氣體流量和溫度等關鍵製程參數,其性能符合文獻中所述的基本等離子體加工要求。這種等級的控制對於可重複的奈米級加工和先進材料研究至關重要。模組化系統架構支援針對特定應用進行客製化,涵蓋化合物半導體、光子裝置、MEMS 以及新興量子技術等領域。

SENTECH 專注於研究和中小規模生產環境,為從早期實驗到可擴展生產的製程開發提供支援。 SENTECH 電漿蝕刻解決方案廣泛應用於全球大學、科研院所和工業生產領域,協助微電子、奈米技術和光電子領域的創新發展,彌合實驗室與工廠之間的鴻溝。

SENTECH 擁有現場等離子和計量應用實驗室,我們的專家團隊為您提供製程優化方面的支持,滿足您的應用需求。您只需聯絡我們的團隊,即可洽談樣品寄送事宜。

結論

電漿體蝕刻仍然是現代半導體製造的基礎技術,它能夠在各種材料和尺寸上實現精確的圖案轉移。從RIE的多功能性、ICP-RIE的高性能,到DRIE實現的極高縱橫比以及ALE的原子級精度,每一種技術都在當今的研究和工業領域中發揮著至關重要的作用。借助SENTECH的先進等離子體蝕刻工具,研究人員和工程師能夠更好地應對下一代半導體、奈米技術和光電裝置的挑戰。